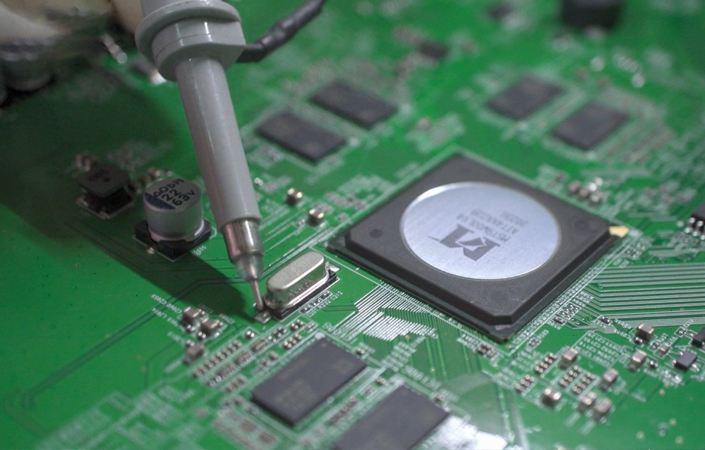

晶体振荡器PCB布局设计指南

在电子设备中,晶体振荡器扮演着非常关键的角色,它是我们设备的时钟源,确保系统的时钟精度和可靠性。为了让晶体振荡器发挥最佳性能,TROQ创捷电子与大家分享以下一些实用的晶体振荡器PCB布局设计指南:

1.选择合适的晶体振荡器:

首先需要选择满足系统需求的晶体振荡器,这主要取决于系统的频率需求、精度、稳定性和功耗等参数。

2.保持振荡器稳定性:

晶体振荡器的稳定性对于系统的时钟精度和可靠性至关重要。在布局设计中,要确保振荡器的两个引脚(一般为晶体的两个引脚)尽可能短且相等的长度,并与晶体连接。这有助于减小引脚之间的差异和串扰,提高振荡器的稳定性。

3.确认微控制器能否驱动晶体振荡器:

在选择好晶体振荡器后,需要确认微控制器是否可以驱动它。如果微控制器无法驱动晶体振荡器,可能需要进行硬件或软件方面的调整。

4.考虑晶体振荡器的功耗:

一般来说,较大的负载电容会导致更高的功耗损耗。因此,在选择晶体振荡器时,需要综合考虑其功耗和性能。

5.降低噪声和干扰:

晶体振荡器对于外部噪声和干扰非常敏感。为了降低噪声和干扰对振荡器的影响,应将其引脚与其他高速信号线隔离。避免将高功率信号线和高噪声源(如开关电源)靠近振荡器引脚。同时,在 PCB 布局中使用地平面层和电源平面层,以提供良好的地和电源引用。

6.合理布局晶体振荡器电路:

应将晶体振荡器放置在靠近微控制器的位置,以减小信号传输延迟。同时,为了防止高频电路对晶振产生干扰,振荡器电路应与高频电路隔离。

7.晶振外壳接地:

为了提高信号质量,应将晶振外壳接地,这可以有效地减小外界电磁干扰。

8.阻抗匹配和信号完整性:

晶体振荡器的引脚通常具有较高的输出阻抗,需要与后续电路匹配。在 PCB 布局中,确保振荡器引脚的阻抗匹配,可以通过合适的 PCB 线宽和间距来实现。此外,使用差分信号线或阻抗控制技术,可以提高信号完整性和减少信号失真。

9.时钟信号走线要短而宽:

时钟信号的走线尽量短,这样可以减少信号传输延迟,提高系统效率;线宽要大一些,可以增加信号强度,提高信号质量。

10.注意焊接温度:

在手工或机器焊接时,要注意焊接温度,避免温度过高损坏晶体振荡器。

11.尽量减少振荡器与其他高速信号线的交叉:

高速信号线的电磁干扰可能会对振荡器的性能产生不利影响。在布局设计中,尽量避免振荡器与其他高速信号线的交叉。如果无法完全避免,可以采取适当的阻隔措施,如增加间距、使用地平面层或屏蔽罩等。

12.耦合电容应靠近晶振的电源管脚放置:

为了提高电源的稳定性,应将耦合电容尽量靠近晶振的电源管脚放置。

13.良好的热管理:

晶体振荡器在工作过程中会产生一定的热量,因此需要良好的热管理。在布局设计中,确保振荡器周围没有阻塞空气流动的元件或散热器,并在必要时考虑导热垫或散热设计。

以上是关于晶体振荡器PCB布局设计的一些实用指南,希望对大家有所帮助。如有其它疑问,欢迎随时提问。TROQ创捷电子专注晶振研发、设计、生产及销售,专业FAE工程师免费提供技术支持。

浙公网安备33071802888965

浙公网安备33071802888965